Scientists from MIT and NVIDIA have created two strategies that speed up the handling of scanty tensors, a sort of information structure that is utilized for elite execution processing undertakings. The corresponding strategies could bring about huge upgrades to the presentation and energy-proficiency of frameworks like the gigantic AI models that drive generative, man-made reasoning.

Tensors are information structures utilized by AI models. Both of the new techniques look to proficiently take advantage of what’s known as sparsity—zero qualities—in the tensors. While handling these tensors, one can skirt the zeros and save money on both calculation and memory. For example, anything duplicated by zero will be zero, so it can avoid that activity. Furthermore, it can pack the tensor (which Zeros doesn’t need to bother with to be put away), so a bigger part can be put away in on-chip memory.

In any case, there are a few difficulties to taking advantage of sparsity. Finding the nonzero values in an enormous tensor is no simple undertaking. Existing methodologies frequently limit the areas of nonzero values by implementing a sparsity example to work on the pursuit; however, this restricts the range of meager tensors that can be handled effectively.

Another test is that the quantity of nonzero values can change in various locales of the tensor. This makes it hard to decide how much space is expected to store various areas in memory. To ensure the district fits, more space is frequently assigned than is required, causing the capacity cradle to be underutilized. This increments off-chip memory traffic, which requires additional calculation.

“When using more specialized or domain-specific hardware accelerators, you typically lose the flexibility provided by a more general-purpose processor, such as a CPU. What distinguishes these two works is that they demonstrate that it is possible to preserve flexibility and adaptation while remaining specialized and efficient.“

Vivienne Sze, associate professor in the MIT Department of Electrical Engineering and Computer Science (EECS),

The MIT and NVIDIA specialists gave two answers to address these issues. For one’s purposes, they fostered a procedure that permits the equipment to proficiently find the nonzero values for a more extensive assortment of sparsity designs.

For the other arrangement, they made a strategy that can deal with the situation where the information doesn’t fit in memory, which builds the usage of the stockpiling cradle and lessens off-chip memory traffic.

The two techniques help the exhibition and diminish the energy requests of equipment with gas pedals explicitly intended to accelerate the handling of inadequate tensors. The papers have been presented on the arXiv preprint server.

“Normally, when you utilize more particular or space-explicit equipment gas pedals, you lose the adaptability that you would get from a more broadly useful processor, similar to a computer chip. What stands apart with these two works is that we demonstrate the way that you can in any case keep up with adaptability and flexibility while being particular and effective,” says Vivienne Sze, academic administrator in the MIT Division of Electrical Designing and Software Engineering (EECS), an individual from the Exploration Lab of Gadgets (RLE), and co-senior creator of papers on the two advances.

Her co-creators incorporate lead creators Yannan Nellie Wu, Ph.D. ’23, and Zi Yu Xue, an electrical designing and software engineering graduate understudy; and co-senior creator Joel Emer, a MIT teacher of training in software engineering and electrical designing and an individual from the Software Engineering and Man-made Brainpower Lab (CSAIL), as well as others at NVIDIA. The two papers will be introduced at the IEEE/ACM Worldwide Discussion on Microarchitecture.

Feature: Productively tracking down zero qualities

Sparsity can emerge in the tensor for different reasons. For instance, scientists at times “prune” superfluous bits of the AI models by supplanting a few qualities in the tensor with zeros, making sparsity. The level of sparsity (level of zeros) and the areas of the zeros can fluctuate for various models.

To make it more straightforward to find the leftover nonzero values in a model with billions of individual qualities, scientists frequently confine the area of the nonzero values so they fall into a specific example. In any case, every equipment gas pedal is ordinarily intended to help with explicit sparsity design, restricting its adaptability.

Conversely, the equipment gas pedal the MIT specialists planned, called Feature, can deal with a wide assortment of sparsity examples and perform well while running models that have no zero qualities.

They utilize a strategy they call “various leveled organized sparsity” to productively address a wide assortment of sparsity designs that are made out of a few basic sparsity designs. This approach isolates the qualities in a tensor into more modest blocks, where each block has its own straightforward, sparse design (maybe two zeros and two nonzeros in a block with four qualities).

Then, they join the blocks into an order, where every assortment of blocks likewise has its own straightforward, sparse design (maybe one zero block and three nonzero blocks in a level with four blocks). They keep consolidating blocks into bigger levels; however, the examples stay basic at each step.

This straightforwardness empowers Feature to all the more effectively find and skip zeros, so it can make the most of the valuable chance to cut abundance calculations. By and large, their gas pedal plan was multiple times more energy-productive than different methodologies.

“Eventually, the Feature gas pedal can effectively speed up thick models since it doesn’t present a ton of above, and simultaneously it can take advantage of responsibilities with various measures of zero qualities in view of progressive organized sparsity,” Wu makes sense of.

Later on, she and her associates need to apply various levels of organized sparsity to additional sorts of AI models and various kinds of tensors in the models.

Tailors and Swiftiles: Actually ‘overbooking’ to speed up jobs

Scientists can likewise use sparsity to more productively move and cycle information on a CPU.

Since the tensors are frequently bigger than whatever can be put away in the memory cradle on the chip, the chip just snatches and cycles a piece of the tensor at a time. The lumps are called tiles.

To expand the use of that cradle and breaking point for the times the chip should access off-chip memory, which frequently overwhelms energy utilization and cutoff points for handling speed, scientists try to utilize the biggest tile that will squeeze into the support.

Be that as it may, in a meager tensor, a significant number of the information values are zero, so a considerably bigger tile can squeeze into the support than one could anticipate in view of its ability. Zero qualities needn’t bother with being put away.

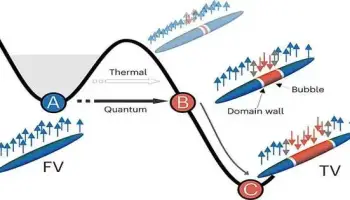

Yet, the quantity of zero qualities can shift across various areas of the tensor, so they can likewise change for each tile. This makes it challenging to decide a tile size that will fit in the cushion. Thus, existing methodologies frequently safely expect there are no zeros and wind up choosing a more modest tile, which brings about squandered clear spaces in the cushion.

To address this vulnerability, the scientists propose the utilization of “overbooking” to permit them to expand the tile size, as well as a method for enduring it on the off chance that the tile doesn’t fit the cushion.

The same way a carrier overbooks tickets for a flight, in the event that every one of the travelers appears, the carrier should remunerate the ones who are knocked off the plane. In any case, generally, every one of the travelers doesn’t appear.

In a meager tensor, a tile size can be picked to such an extent that typically the tiles will have an adequate number of zeros that generally still fit into the support. Yet, periodically, a tile will have more nonzero values than will fit. In this situation, those details are knocked out of the support.

The specialists empower the equipment to just re-bring the knock information without getting and handling the whole tile once more. They change the “last part” of the cushion to deal with this, thus the name of this strategy, Designers.

Then they likewise developed a methodology for finding the size of tiles that exploits overbooking. This strategy, called Swiftiles, quickly gauges the ideal tile size, so a particular level of tiles, set by the client, is overbooked. (The names “Designers” and “Swiftiles” give proper respect to Taylor Quick, whose new Periods visit was full of overbooked presale codes for tickets.)

Swiftiles reduces the time the equipment needs to actually look at the tensor to recognize an ideal tile size, saving money on calculation. The blend of Designers and Swiftiles dramatically increases the speed while requiring just around 50% of the energy requests of existing equipment gas pedals, which can’t deal with overbooking.

“Swiftiles permit us to assess how enormous these tiles should be without requiring various emphases to refine the gauge. This main works on the grounds that overbooking is upheld. Regardless of whether you are off by a respectable sum, you can in any case extricate a fair piece of speedup due to how the non-zeros are conveyed,” Xue says.

Later on, the specialists need to apply the possibility of overbooking to different angles in PC engineering and, furthermore, work on the cycle for assessing the ideal degree of overbooking.

More information: Zi Yu Xue et al., Tailors: Accelerating Sparse Tensor Algebra by Overbooking Buffer Capacity, arXiv (2023). DOI: 10.48550/arxiv.2310.00192