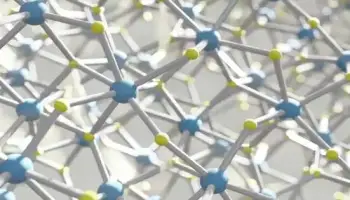

The potential for integrating energy-efficient photonics with cost-effective electronics has recently been unlocked by researchers at the Hong Kong University of Science and Technology (HKUST). They have created a novel integration scheme for efficient coupling between III-V compound semiconductor devices and silicon components on a silicon photonics (Si-photonics) platform by selective direct epitaxy. Over the past few years, data traffic has been growing exponentially driven by various applications and emerging techniques such as big data, automobiles, cloud applications, and sensors.

Si-photonics has received a lot of attention as a key technology to enable, extend, and boost data transfer through cost-effective, high-capacity optical interconnects.

While silicon-based passive components are well established on the Si-photonics platform, silicon cannot be used to create lasers or photodetectors, hence other materials, such as III-V compound semiconductors, must be integrated on silicon.

There are two primary ways that III-V lasers and photodetectors on silicon have been studied. The first is the bonding-based approach, which has produced impressively performing gadgets.

However, it necessitates a complex manufacturing process with a poor yield and high cost, making mass production extremely difficult. The alternative is to develop many layers of III-V on silicon using the direct epitaxy approach.

Although it offers a lower cost, more scalable, and greater integration density solution, the micrometer-thick III-V buffer layers that are essential for this technology obstruct effective light coupling between III-V and silicon, which is essential for integrated Si-photonics.

This was made possible by our latest development of a novel growth technique named lateral aspect ratio trapping (LART) and our unique design of coupling strategy on the SOI platform. Our team’s combined expertise and insights into both device physics and growth mechanisms allow us to accomplish the challenging task of efficient coupling between III-V and Si and cross-correlated analysis of epitaxial growth and device performance.

Professor Kei-May LAU

To address these issues, the team led by Prof. Kei-May LAU, Professor Emeritus of the Department of Electronic and Computer Engineering at Hong Kong University of Science and Technology (HKUST), developed lateral aspect ratio trapping (LART) a novel selective direct epitaxy method that can selectively grow III-V materials on silicon-on-insulator (SOI) in a lateral direction without the need of thick buffers.

Additionally, the team developed and demonstrated a special in-plane integration of III-V photodetectors and silicon elements with high coupling efficiency between III-V and silicon-based on this revolutionary technology.

With a record-high speed of over 112 Gb/s, way faster than existing products, the performance of photodetectors using such an approach is less noisy, more sensitive, and has a wider operating range.

Direct epitaxy allows the III-V devices to link successfully with Si elements for the first time. The ultimate objective of integrating photonics with electronics on a silicon photonics platform for data communications is made possible by the integration strategy, which can be easily applied to the integration of various III-V devices and Si-based components.

“This was made possible by our latest development of a novel growth technique named lateral aspect ratio trapping (LART) and our unique design of coupling strategy on the SOI platform. Our team’s combined expertise and insights into both device physics and growth mechanisms allow us to accomplish the challenging task of efficient coupling between III-V and Si and cross-correlated analysis of epitaxial growth and device performance,” said Prof. Lau.

“This work will provide practical solutions for photonic integrated circuits and fully integrated Si-photonics, light coupling between III-V lasers and Si components can be realized through this method,” said Dr. Ying Xue, first author of the study.

This is a collaborative work with a research team led by Prof. Hon Ki Tsang of the Department of Electronic Engineering at Chinese University of Hong Kong (CUHK) and a research team led by Prof. Xinlun Cai of School of Electronics and Information Technology at Sun Yat-sen University (SYSU).

The device fabrication technology in the work was developed at HKUST’s Nanosystem Fabrication Facility (NFF) on Clear Water Bay campus. Research Grants Council of Hong Kong and the Innovation Technology Fund of Hong Kong supports the work. This work has recently been published in Optica.