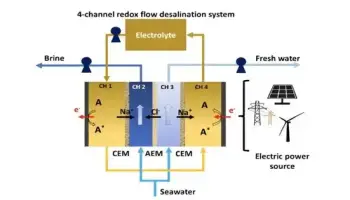

Engineers at Caltech and the University of Southampton in the United Kingdom collaborated to design a gadget chip that is coordinated with a photonics chip (which uses light to move information), resulting in a firm end result capable of sending data at ultrahigh speed while producing negligible intensity.

However, the two-chip sandwich is probably not going to find its way into your PC, and the new plan could impact the fate of server farms that oversee extremely high volumes of information correspondence.

“Each time you are on a video call, transfer a film, or play a web-based computer game, you’re directing information to and fro through a server farm to be handled,” says Caltech graduate understudy Arian Hashemi Talkhooncheh, lead creator of a paper depicting the two-chip development that was distributed in the IEEE Diary of Strong State Circuits on November 3.

“The speed of data connection between multiple processors is constantly growing, not just in data centers but also in high-performance computers. As chip computing capacity increases, communication speed can become a bottleneck, especially when energy is limited.”

Azita Emami, the Andrew and Peggy Cherng Professor of Electrical Engineering and Medical Engineering;

“There are in excess of 2,700 server farms in the U.S. and more than 8,000 around the world, with pinnacles of servers stacked on top of one another to deal with the heap of thousands of terabytes of information going in and out each second.”

Similarly to how your PC warms up on your lap while you use it, the pinnacles of servers in server farms that keep us all connected heat up as well, albeit on a much larger scale.Several server farms have even been submerged in order to effectively cool entire offices.The more productive they can be, the less intensity they will create, and finally, the greater the volume of data that they will want to make due.

Information handling is finished on electronic circuits, while information transmission is most efficiently done utilizing photonics. It is extremely difficult to achieve ultrahigh speed in every space, but designing the connection point between them is far more difficult.

“There is a consistent interest in speeding up information correspondence between various chips in server farms as well as in elite execution PCs.” “As the processing force of the chips scales, the correspondence speed can turn into the bottleneck, particularly under rigid energy requirements,” says Azita Emami, the Andrew and Peggy Cherng Teacher of Electrical Designing and Clinical Designing, top dog for electrical design, and senior creator of the paper.

To address this test, the Caltech/Southampton group planned both a hardware chip and a photonics chip starting from the earliest stage and jointly improved them to cooperate. The cycle, from the underlying plan to the last test in the lab, required four years to finish, with each plan decision affecting the two chips.

“We needed to streamline the whole framework all at once, which empowered accomplishing a prevalent power proficiency,” Hashemi says. “These two chips are, in a real sense, made for each other, coordinated in three aspects.”

The subsequent improved interface between the two chips permits them to communicate 100 gigabits of information each second while delivering just 2.4 picojoules per sent piece. This improves the transmission’s electro-optical power proficiency by a factor of 3.6 when compared to the current state of the workmanship.A picojoule is one-trillionth of a joule, which is characterized as the energy delivered in one moment by a current of 1 ampere through an obstruction of 1 ohm—or around 0.24 calories.

“As the world turns out to be increasingly associated and each gadget creates more information, it is energizing to demonstrate the way that we can accomplish such high information rates while consuming a negligible portion of force compared with the customary procedures,” says Emami.

The paper is titled “A 100 Gb/s PAM4 Optical Transmitter in a 3D-Coordinated SiPh-CMOS Stage Utilizing Divided MOSCAP Modulators.”

More information: Arian Hashemi Talkhooncheh et al, A 100-Gb/s PAM4 Optical Transmitter in a 3-D-Integrated SiPh-CMOS Platform Using Segmented MOSCAP Modulators, IEEE Journal of Solid-State Circuits (2022). DOI: 10.1109/JSSC.2022.3210906

Journal information: IEEE Journal of Solid-State Circuits